Level Trigger:

1) The input signal is sampled when the clock signal is either HIGH or LOW.

2) It is sensitive to Glitches.

Example: Latch.

Edge Trigger:

1) The input signal is sampled at the RISING EDGE or FALLING EDGE of the clock signal.

2) It is not-sensitive to Glitches.

Example: Flipflop.

1) The input signal is sampled when the clock signal is either HIGH or LOW.

2) It is sensitive to Glitches.

Example: Latch.

Edge Trigger:

1) The input signal is sampled at the RISING EDGE or FALLING EDGE of the clock signal.

2) It is not-sensitive to Glitches.

Example: Flipflop.

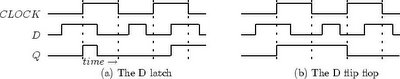

I m sure the timing diagrams below is the best way of explanation.

Courtesy: www.wiki.answers.com

thanks. if you can elaborate it will be more helpful.

ReplyDeletelactches not used clock they use en input

ReplyDeleteThanks!!!

ReplyDeleteit will be the best if you can explain the diagram

ReplyDeleteIt will be useful if the "leading" and "trailing" edges are also marked since some textbooks prefer to use these terms.

ReplyDeleteNot a useful answer. Try to explain what is happening and not just talk jargon.

ReplyDeleteI have always had difficulty in figuring out which is the leading edge and which is the trailing edge in a pulse train and textbooks like Millman and Taub don't make clear which is the leading edge and which is the trailing edge.

DeleteThis is an awesome article a debt of gratitude is in order for sharing this instructive data. I will visit your website routinely for some most recent post. I will visit your website frequently for Some most recent post. camping generators

ReplyDeleteStay on top of the market with our Live, Real-Time Stock Market overview. Get real time Fxit Stock quotes and interactive charts.

ReplyDelete